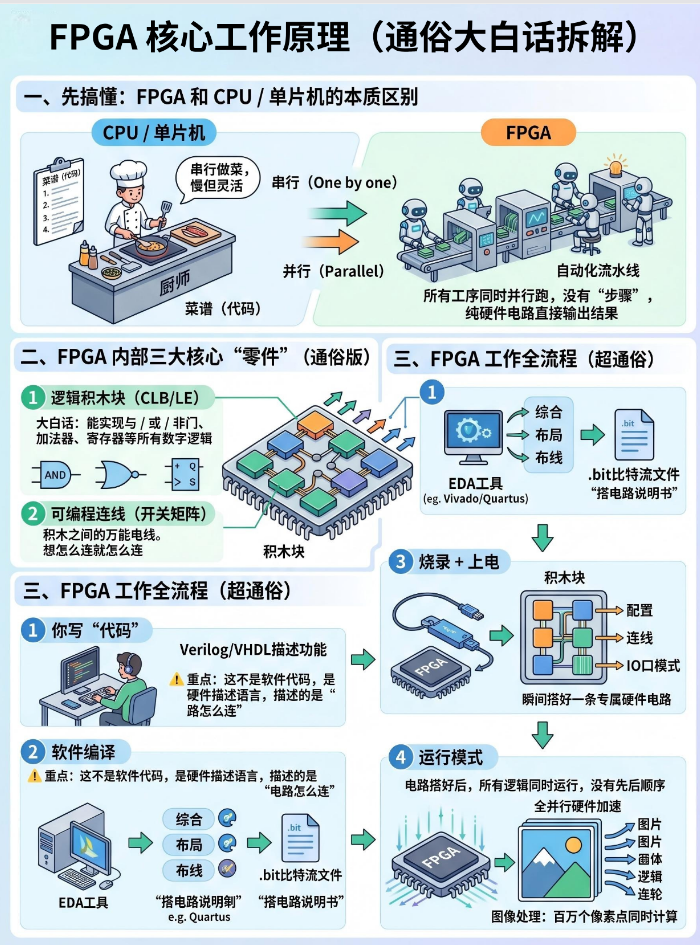

一、先搞懂:FPGA 和 CPU / 单片机的本质区别

CPU / 单片机:像厨师,手里只有一套工具,按菜谱(代码)一步一步串行做菜,慢但灵活。

FPGA:像直接搭建一条自动化流水线,所有工序同时并行跑,没有 “步骤”,纯硬件电路直接输出结果。

二、FPGA 内部三大核心 “零件”(通俗版)

FPGA 内部就是一堆可自由拼接的电子积木,主要 3 部分:

1、逻辑积木块(CLB/LE)

。大白话:能实现与 / 或 / 非门、加法器、寄存器等所有数字逻辑,想算什么逻辑就配置成什么。

2、可编程连线(开关矩阵)

积木之间的万能电线。

你想把 A 积木连 B 积木,还是连 C 积木,全靠它自由切换,想怎么连就怎么连。

3、可编程 IO 口

对外的接口插头。

接传感器、屏幕、摄像头、DDR、PCIe 等,电平、功能都能改。

三、FPGA 工作全流程(超通俗)

1. 你写 “代码” → 其实是画电路图纸

用 Verilog/VHDL 描述功能(比如 “让 LED 闪烁”“解码图像”)。

⚠️ 重点:这不是软件代码,是硬件描述语言,描述的是 “电路怎么连”。

2. 软件编译 → 生成 “搭建说明书”

EDA 工具(Vivado/Quartus)做 3 件事:

综合:把你的描述转成逻辑门连接关系

布局:把逻辑门分配到 FPGA 内部积木块

布线:把积木块用可编程连线连起来

最终生成比特流文件(.bit),这就是 FPGA 的 “搭电路说明书”。

3. 烧录 + 上电 → 直接搭出专用硬件

FPGA 上电后,读取比特流:

配置逻辑积木块功能

接通对应可编程连线

配置 IO 口模式

✅ 瞬间搭好一条专属硬件电路,没有 CPU 那种取指、译码、执行,电路直接通电运行。

4. 运行模式 → 全并行硬件加速

电路搭好后,所有逻辑同时运行,没有先后顺序。

比如处理图像:百万个像素点同时计算,速度比 CPU 快几十上百倍。

未经许可,禁止转载!

下一篇:没有了